隨著便攜式設備、物聯網節點和可穿戴技術的飛速發展,對模擬集成電路(Analog IC)的性能、功耗和尺寸提出了前所未有的挑戰。其中,低電壓系統的設計與實現成為核心技術之一。它要求在更低的電源電壓下,確保模擬電路(如放大器、濾波器、數據轉換器)仍能維持足夠的性能、動態范圍和信噪比。這不僅涉及精密的電路設計,更與電源管理單元(PMU)的設計和配套的軟件開發緊密相連。

一、低電壓模擬IC設計的核心挑戰

在傳統的高電壓供電系統中,設計者有充足的電平裕度來處理信號擺幅和噪聲容限。當電源電壓降至1V甚至更低時(例如采用先進工藝節點),設計面臨嚴峻考驗:

- 信號擺幅受限:低電源電壓直接壓縮了模擬信號的線性輸出范圍,可能降低動態范圍和信噪比(SNR)。

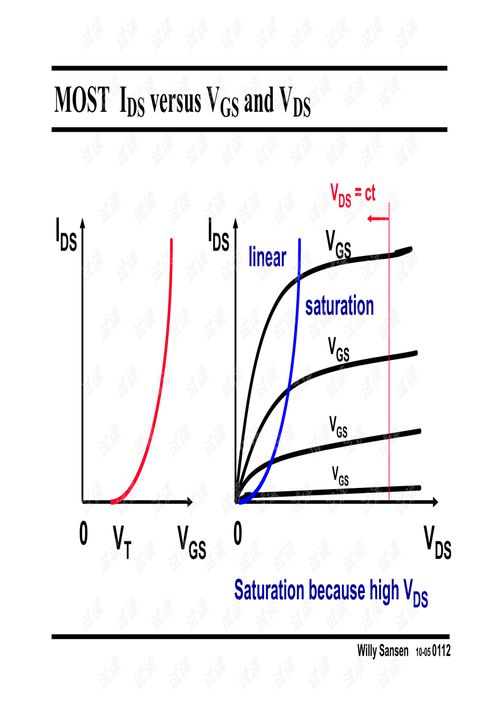

- 閾值電壓影響凸顯:MOSFET的閾值電壓(Vth)并未隨工藝按比例縮小,導致有效過驅動電壓(Vgs-Vth)大幅減少,影響增益、帶寬和匹配精度。

- 噪聲與電源抑制比(PSRR):電源噪聲和襯底噪聲的影響相對增大,對電源的純凈度和穩定性要求更高。

二、電源設計的關鍵應用

為應對上述挑戰,電源設計必須從“粗放供電”轉向“精準協同”。主要應用方向包括:

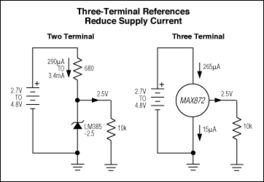

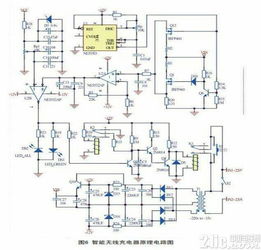

- 高效低噪聲低壓差線性穩壓器(LDO):雖然開關電源(DC-DC)效率更高,但其開關噪聲對敏感的模擬電路可能是災難性的。因此,常采用“DC-DC + LDO”的級聯結構,由DC-DC進行初步降壓并保證效率,再由超低噪聲、高PSRR的LDO提供“清潔”的模擬電源。LDO的設計需特別關注其噪聲譜密度和瞬態響應能力。

- 多域電源管理:復雜的模擬混合信號系統(如SoC)常包含多個電源域(Power Domain)。例如,為高精度的模數轉換器(ADC)或壓控振蕩器(VCO)提供獨立的、高度穩定的電源,以隔離數字開關噪聲。這需要精密的電源門控、時序控制和電平轉換電路。

- 動態電壓與頻率調節(DVFS):對于對功耗極度敏感的應用,系統可根據性能需求動態調節模擬模塊(或與之關聯的數字邏輯)的供電電壓和工作頻率,在能效和性能間取得最佳平衡。

三、軟件開發的協同作用

現代模擬集成電路的電源系統已不再是純粹的硬件問題。軟件,特別是固件(Firmware)和系統控制軟件,扮演著越來越重要的“大腦”角色:

- 配置與校準:軟件可通過數字接口(如I2C、SPI)配置PMU內部的寄存器,靈活設置各電源軌的輸出電壓、上電/掉電時序(Power Sequencing)、過流保護閾值等。這對于滿足不同工作模式(如待機、活躍、高性能模式)至關重要。軟件還可驅動芯片執行上電自檢和校準流程,補償工藝偏差帶來的性能誤差。

- 狀態監控與診斷:集成在PMU或模擬模塊內部的傳感器(如溫度傳感器、電流檢測放大器)可將數據反饋給軟件。軟件可實時監控系統健康狀況,實現預測性維護或在異常時安全關閉相關模塊。

- 智能能量管理算法:在系統層面,操作系統(OS)或專用的電源管理中間件可以根據應用負載、電池狀態和環境條件,運行復雜的算法,動態決策各模塊的最佳電壓/頻率工作點(DVFS),實現全局最優的能效管理。

四、未來趨勢

模擬IC的低電壓設計將與電源管理和軟件更深地融合:

- 工藝協同優化:設計工藝庫將更加注重低電壓下的器件模型精度和可靠性。

- 集成化與智能化:PMU將集成更多功能(如電池管理、能量收集接口)并內置可編程狀態機,減輕主機處理器的負擔。

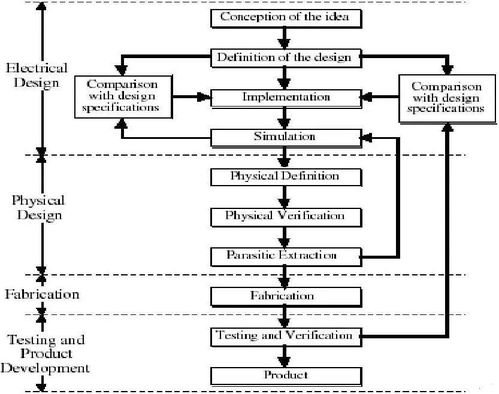

- 設計自動化工具:EDA工具將更緊密地集成電路仿真、電源完整性分析和軟件配置代碼生成,實現跨領域的協同設計與驗證。

結論

模擬集成電路的低電壓系統是一項系統工程,它要求硬件工程師與軟件開發者打破藩籬,緊密協作。卓越的電源設計為高性能模擬電路提供了穩定、純凈的能量基礎,而智能的軟件則賦予了系統靈活、自適應和高效管理能量的智慧。兩者相輔相成,共同推動著下一代低功耗、高性能電子設備的發展。