在當(dāng)今高度集成的電子系統(tǒng)中,單電源供電已成為主流趨勢(shì),因其能夠簡(jiǎn)化電源管理、降低成本并減少系統(tǒng)體積。CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)集成電路以其低功耗、高噪聲容限和易于集成的優(yōu)勢(shì),成為實(shí)現(xiàn)單電源接口電路設(shè)計(jì)的理想選擇。本文將探討基于CMOS技術(shù)的單電源接口電路設(shè)計(jì)原理、關(guān)鍵模塊及設(shè)計(jì)考量。

一、 單電源接口電路設(shè)計(jì)基礎(chǔ)

單電源接口電路的核心挑戰(zhàn)在于處理信號(hào)擺幅和共模電平的兼容性。在單電源供電(例如+5V或+3.3V)下,信號(hào)的動(dòng)態(tài)范圍被限制在0V至VDD之間。而許多傳感器、外部器件或通信標(biāo)準(zhǔn)(如RS-232傳統(tǒng)電平)產(chǎn)生的信號(hào)可能包含負(fù)電壓或超出此范圍的電壓。因此,接口電路必須完成電平轉(zhuǎn)換、信號(hào)調(diào)理和阻抗匹配等功能,同時(shí)確保自身在單電源下穩(wěn)定工作。

CMOS技術(shù)在此類設(shè)計(jì)中展現(xiàn)出獨(dú)特優(yōu)勢(shì):

- 寬電源電壓范圍:許多CMOS工藝支持較寬的VDD范圍,便于適應(yīng)不同的單電源標(biāo)準(zhǔn)。

- 軌到軌(Rail-to-Rail)輸入/輸出能力:通過特殊設(shè)計(jì)的輸入級(jí)和輸出級(jí),CMOS運(yùn)放和邏輯電路可以實(shí)現(xiàn)輸入和輸出電壓非常接近電源軌(0V和VDD),最大化信號(hào)動(dòng)態(tài)范圍。

- 高輸入阻抗:CMOS器件的柵極輸入阻抗極高,對(duì)前級(jí)電路的負(fù)載效應(yīng)極小,有利于信號(hào)采集。

二、 關(guān)鍵電路模塊設(shè)計(jì)

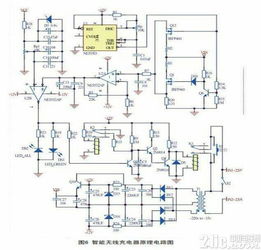

一個(gè)典型的單電源接口電路通常包含以下幾個(gè)關(guān)鍵模塊:

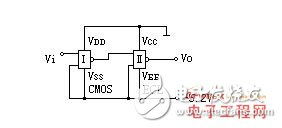

1. 電平移位器(Level Shifter):

這是處理不同邏輯電平(如1.8V CMOS與3.3V TTL)之間接口的核心。設(shè)計(jì)時(shí)需考慮電壓轉(zhuǎn)換方向、速度及功耗。常用結(jié)構(gòu)包括使用串聯(lián)NMOS/PMOS對(duì)、交叉耦合鎖存器或基于運(yùn)放的加法器電路,確保信號(hào)在0-VDD范圍內(nèi)被準(zhǔn)確平移和整形。

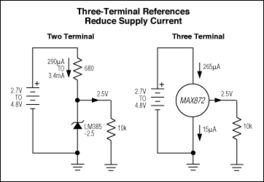

2. 單電源運(yùn)算放大器接口:

用于模擬信號(hào)調(diào)理(如放大、濾波)。設(shè)計(jì)重點(diǎn)在于設(shè)置合適的直流偏置點(diǎn)(通常為VDD/2),以確保交流信號(hào)在單電源下能以該點(diǎn)為參考進(jìn)行雙向擺動(dòng)。這通常通過電阻分壓網(wǎng)絡(luò)或?qū)S没鶞?zhǔn)電壓源(如帶隙基準(zhǔn))實(shí)現(xiàn)。輸入級(jí)需采用軌到軌或偽軌到軌結(jié)構(gòu)以接收地電位附近的信號(hào)。

3. 模擬開關(guān)與多路復(fù)用器:

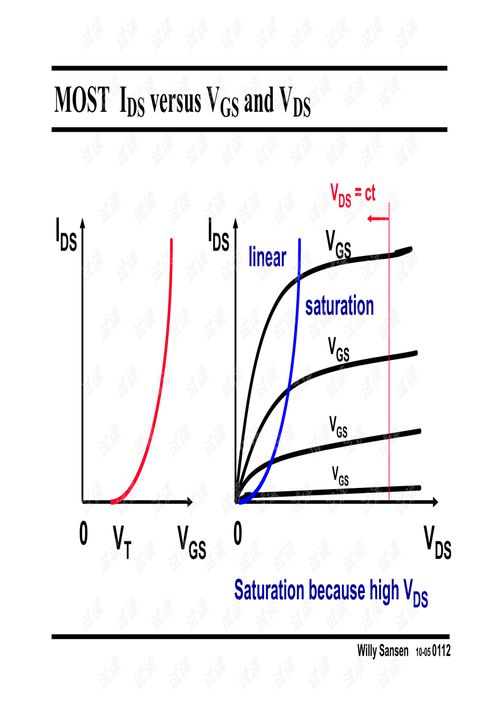

在CMOS工藝中,模擬開關(guān)由MOSFET構(gòu)成,其導(dǎo)通電阻(RON)和開關(guān)速度是關(guān)鍵參數(shù)。單電源設(shè)計(jì)需確保開關(guān)在全部輸入信號(hào)范圍內(nèi)(0-VDD)都能保持低且平坦的RON,并注意電荷注入和時(shí)鐘饋通效應(yīng)的影響。

4. 輸入/輸出(I/O)緩沖器:

用于驅(qū)動(dòng)外部負(fù)載(如LED、繼電器或傳輸線)。設(shè)計(jì)需提供足夠的驅(qū)動(dòng)電流,同時(shí)具備過壓保護(hù)、靜電放電(ESD)防護(hù)和緩變邊沿控制(以減少EMI)。在單電源下,輸出級(jí)常采用推挽(Push-Pull)CMOS結(jié)構(gòu)以實(shí)現(xiàn)接近電源軌的輸出擺幅。

三、 設(shè)計(jì)考量與挑戰(zhàn)

- 電源噪聲與去耦:?jiǎn)坞娫聪到y(tǒng)對(duì)電源噪聲更敏感,尤其是在模擬電路部分。必須在VDD和地之間靠近芯片電源引腳處放置適當(dāng)容值的去耦電容,以濾除高頻噪聲并提供局部電荷儲(chǔ)備。

- 信號(hào)完整性:?jiǎn)坞娫聪拢盘?hào)的地電位參考至關(guān)重要。需要精心設(shè)計(jì)接地策略(如模擬地、數(shù)字地分離并通過單點(diǎn)連接),避免地彈噪聲影響敏感模擬接口。對(duì)于高速接口,還需考慮阻抗匹配和傳輸線效應(yīng)。

- 功耗與性能權(quán)衡:雖然CMOS靜態(tài)功耗低,但在接口電路頻繁切換時(shí),動(dòng)態(tài)功耗不可忽視。設(shè)計(jì)時(shí)需根據(jù)應(yīng)用需求優(yōu)化電路結(jié)構(gòu)(如選擇適當(dāng)?shù)尿?qū)動(dòng)強(qiáng)度、采用時(shí)鐘門控)以平衡速度與功耗。

- 工藝角與可靠性:設(shè)計(jì)必須考慮工藝偏差、溫度變化和電源電壓波動(dòng)對(duì)電路性能(如偏置點(diǎn)、增益、延遲)的影響,通過仿真覆蓋各種極端條件(Corner Case),并留出足夠的設(shè)計(jì)余量。

四、

基于CMOS集成電路的單電源接口電路設(shè)計(jì)是現(xiàn)代電子系統(tǒng)實(shí)現(xiàn)高效、緊湊互聯(lián)的關(guān)鍵。通過充分利用CMOS技術(shù)的優(yōu)勢(shì),并精心設(shè)計(jì)電平移位、信號(hào)調(diào)理、驅(qū)動(dòng)保護(hù)等模塊,可以有效解決單電源環(huán)境下的信號(hào)兼容性問題。成功的接口設(shè)計(jì)不僅需要深入理解電路原理,還需綜合考慮噪聲、功耗、工藝和可靠性等系統(tǒng)級(jí)因素,從而在芯片層面實(shí)現(xiàn)穩(wěn)定、魯棒且成本優(yōu)化的接口解決方案。隨著CMOS工藝的不斷進(jìn)步,未來單電源接口電路將向著更低電壓、更高速度和更智能集成的方向持續(xù)發(fā)展。