引言:VHDL與集成電路設計

VHDL(VHSIC Hardware Description Language,超高速集成電路硬件描述語言)是電子設計自動化(EDA)領域的基石,專門用于描述、模擬和驗證數字電路的行為與結構。隨著集成電路(IC)設計日益復雜,掌握VHDL已成為硬件工程師、FPGA開發者和IC設計師的必備技能。本教程旨在引導初學者理解VHDL在集成電路設計中的應用,并介紹相關電子資源,幫助您高效入門。

第一部分:VHDL基礎與設計流程

1.1 VHDL的核心概念

VHDL是一種并發語言,能描述電路在時間維度上的行為。其基本結構包括實體(Entity,定義接口)、結構體(Architecture,描述功能)、以及進程(Process,用于時序邏輯)。學習VHDL的第一步是理解這些模塊如何協同工作,例如:`vhdl

ENTITY andgate IS

PORT (a, b : IN BIT; c : OUT BIT);

END ENTITY;

ARCHITECTURE behavior OF andgate IS

BEGIN

c <= a AND b; -- 并發賦值語句

END ARCHITECTURE;`

此代碼描述了一個簡單的與門,展示了VHDL如何映射到實際硬件邏輯。

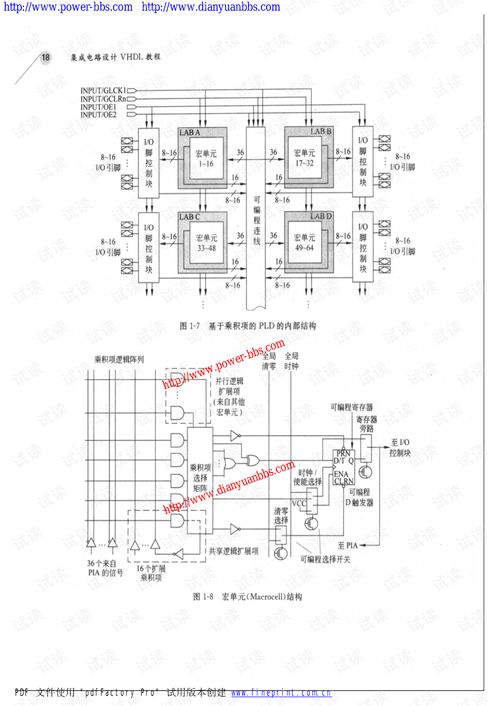

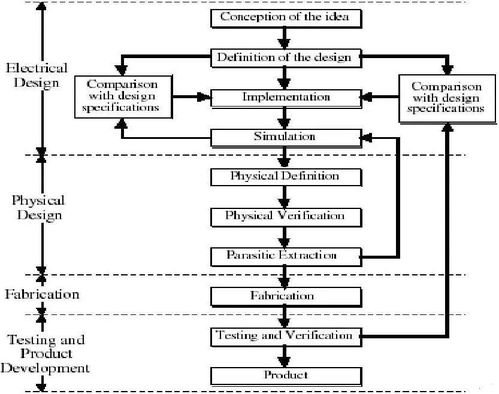

1.2 集成電路設計流程

使用VHDL進行IC設計通常遵循標準化流程:

- 設計輸入:用VHDL代碼描述電路功能。

- 功能仿真:通過工具(如ModelSim)驗證邏輯正確性。

- 邏輯綜合:將代碼轉換為門級網表,優化面積和時序。

- 布局布線:在物理芯片上實現電路連接。

- 時序驗證:確保電路滿足性能要求。

VHDL貫穿始終,尤其在前期設計和驗證中起關鍵作用。

第二部分:VHDL在集成電路設計中的應用

2.1 描述復雜系統

VHDL支持層次化設計,允許將大型IC(如微處理器)分解為模塊(如ALU、寄存器文件),分別編寫代碼再集成。例如,一個計數器模塊可以實例化到更復雜的控制單元中,提升設計可維護性。

2.2 仿真與測試

通過編寫測試平臺(Testbench),設計師能模擬輸入信號并觀察輸出,提前發現錯誤。這在IC制造前至關重要,能節省成本和時間。VHDL的斷言(Assert)語句常用于自動化驗證。

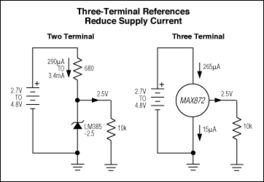

2.3 可綜合代碼實踐

并非所有VHDL代碼都能轉換為硬件。設計IC時,需遵循可綜合子集規則,如避免使用after延遲語句,優先使用寄存器傳輸級(RTL)描述。例如,用進程描述時鐘觸發的D觸發器:`vhdl

PROCESS (clk)

BEGIN

IF rising_edge(clk) THEN

q <= d; -- 同步邏輯

END IF;

END PROCESS;`

第三部分:電子版資源與學習建議

3.1 推薦教程與書籍

- 入門書籍:《VHDL編程實例詳解》(電子版廣泛流通)提供基礎示例;《Digital Design and Computer Architecture》結合VHDL與計算機體系結構。

- 在線課程:Coursera或edX上的“FPGA和IC設計”專項課程常包含VHDL模塊,適合交互學習。

- 官方文檔:IEEE Std 1076標準文檔是權威參考,可在IEEE Xplore獲取電子版。

3.2 實用工具與社區

- 仿真工具:ModelSim(學生版免費)、GHDL(開源)支持VHDL仿真,適用于個人學習。

- 綜合工具:Xilinx Vivado或Intel Quartus提供免費版本,用于FPGA原型設計,是IC設計的前期練習平臺。

- 社區論壇:Stack Exchange的Electrical Engineering板塊、開源硬件社區(如OpenCores)提供代碼分享和問題解答。

3.3 學習路徑建議

1. 從基礎開始:先掌握VHDL語法和簡單電路(如加法器、狀態機)。

2. 項目驅動:通過小項目(如設計一個交通燈控制器)鞏固知識,逐步接觸時序約束和優化。

3. 結合實踐:使用EDA工具運行仿真,對比理論結果;參與開源IC項目(如基于RISC-V的處理器設計)以深入理解行業應用。

結論

VHDL作為集成電路設計的核心語言,不僅賦能工程師描述復雜硬件,還通過仿真和綜合工具貫穿現代IC開發全周期。利用豐富的電子資源(從教程到開源工具),學習者可以系統掌握VHDL,并將其應用于從FPGA到ASIC的實際設計中。隨著物聯網和人工智能推動硬件創新,精通VHDL將成為進入高端電子領域的重要通行證。持續實踐、參與社區交流,將加速您在這一領域的成長。