超大規模集成電路(VLSI)的設計是一個極其復雜且高度系統化的工程過程,其核心目標是將數百萬乃至數十億個晶體管及互連線,按照特定的功能與性能要求,精準地集成到一塊微小的硅片上。本部分將深入探討集成電路設計的基本流程、主要設計方法以及各個設計階段的關鍵任務。

一、集成電路設計的基本流程

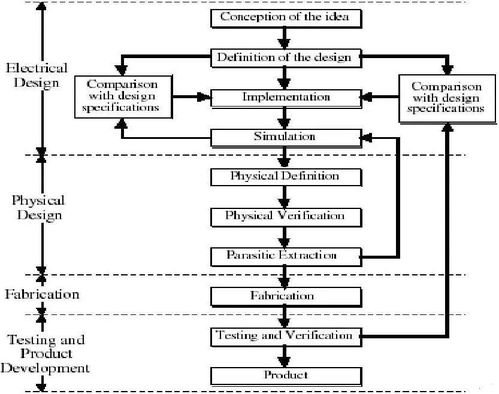

集成電路設計通常遵循一個分層化、模塊化的設計流程,主要可以劃分為以下幾個關鍵階段:

- 系統規劃與行為級描述:這是設計的起點。設計者根據芯片需要完成的功能(如數據處理、信號傳輸等),進行系統級的架構劃分和性能指標定義。通常使用高級硬件描述語言(如SystemVerilog、SystemC)或數學建模工具對系統的整體行為進行抽象描述和仿真驗證。

- 邏輯設計:將行為級描述轉換為由基本邏輯門(如與門、或門、非門、觸發器等)構成的網表。這一階段的核心任務是邏輯綜合,即利用綜合工具,在滿足時序、面積、功耗等約束條件下,將寄存器傳輸級(RTL)代碼自動優化并映射到目標工藝庫的標準邏輯單元上,生成門級網表。

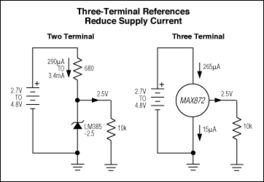

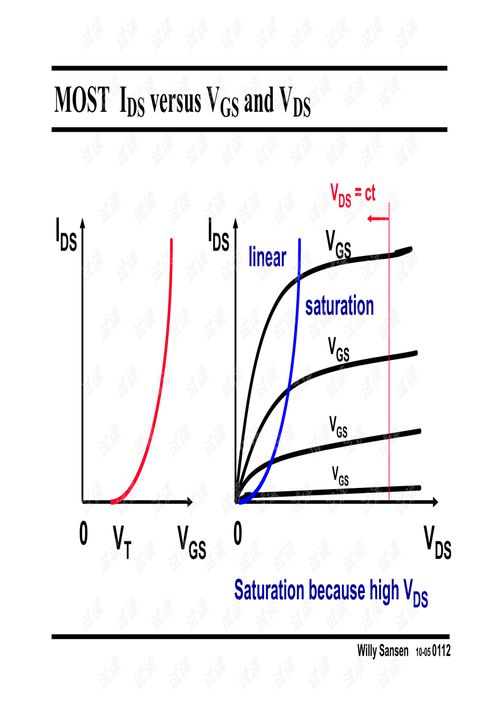

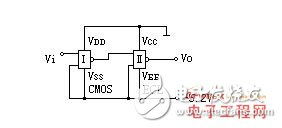

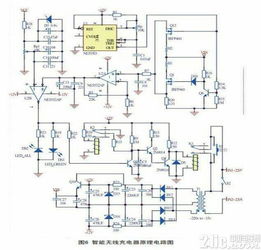

- 電路設計:將門級網表進一步細化到晶體管級。設計者需要確定每個邏輯門的晶體管尺寸、連接方式以及驅動能力,確保電路在速度、功耗和噪聲容限之間取得平衡。對于高性能或模擬電路模塊,此階段往往需要手工精心設計。

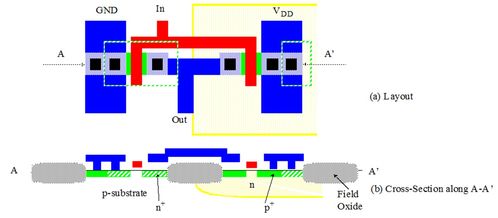

- 物理設計:這是將電路網表轉化為實際幾何版圖(Layout)的過程,是連接設計與制造的橋梁。主要包括:

- 布圖規劃與布局:確定芯片上各個功能模塊(如CPU核、內存、接口)的大致位置和形狀,以及所有標準單元的擺放位置,目標是優化布線資源、縮短關鍵路徑延時。

- 時鐘樹綜合:構建一個低偏斜、低功耗的全局時鐘分布網絡,確保時鐘信號能夠幾乎同步地到達所有時序單元。

- 布線:根據電路的電氣連接關系,在遵守設計規則的前提下,完成所有單元之間金屬連線的物理路徑規劃。

- 物理驗證:對生成的版圖進行設計規則檢查(DRC)、電氣規則檢查(ERC)和版圖與電路圖一致性檢查(LVS),確保其符合代工廠的工藝要求和設計的電氣功能。

- 驗證與簽核:貫穿于整個設計流程。除了各階段的功能仿真,在物理設計完成后,還需要進行包含實際寄生參數(電阻、電容)的后仿真,以及靜態時序分析(STA)、電源完整性分析、信號完整性分析等,以確保芯片在真實物理條件下能夠正確、可靠地工作,最終達到可以交付制造的“簽核”標準。

二、主要設計方法

面對VLSI的復雜性,工程師主要采用兩種互補的設計方法:

- 自頂向下設計:這是主流的設計范式。從最高抽象級別的系統規格開始,逐層進行功能分解和細化,直至底層的物理實現。每一層都進行建模、仿真和驗證,確保下層實現符合上層的功能定義。這種方法有利于管理復雜性,提高設計重用性,并支持團隊并行開發。

- 自底向上設計:基于已有的、經過驗證的底層單元(如標準邏輯單元、存儲器編譯器生成的模塊、IP核等)來構建更復雜的系統。在基于標準單元庫和IP復用的現代設計中,物理設計階段很大程度上是自底向上的。通常,自頂向下和自底向上的方法會在設計流程中結合使用。

三、現代設計的關鍵支撐技術

- 電子設計自動化工具:EDA工具鏈是VLSI設計的生命線,涵蓋了從仿真、綜合、布局布線到驗證的所有環節,極大地提升了設計效率和可靠性。

- 知識產權核復用:廣泛使用經過預設計、預驗證的IP核(如處理器核、接口控制器、存儲器等),是快速構建復雜SoC芯片的基石。

- 可制造性設計:在設計中預先考慮制造工藝的波動和限制,通過添加冗余結構、優化圖形等方式,提高芯片的良率和可靠性。

超大規模集成電路設計是一個融合了系統架構、微電子學、計算機科學和精密工程的綜合性學科。其嚴謹的分層設計流程與先進的EDA方法學,共同構成了將創新思想轉化為硅片上現實功能的堅實橋梁。理解這一完整的設計脈絡,是深入VLSI領域的基礎。