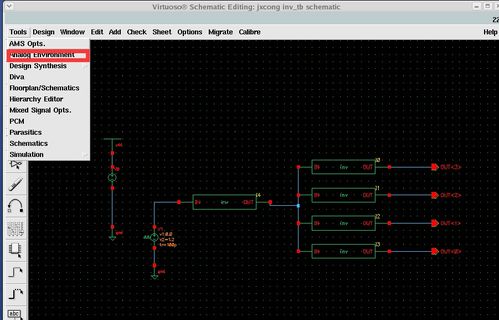

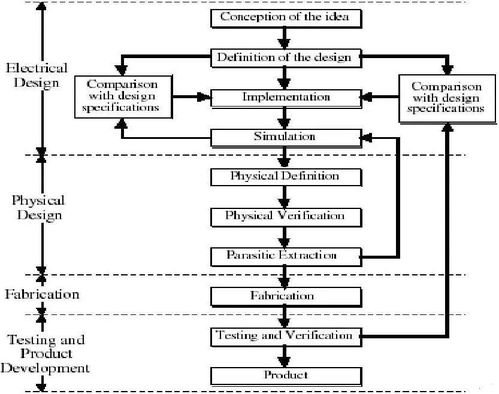

在數(shù)字集成電路設(shè)計(jì)流程中,版圖設(shè)計(jì)是將電路原理圖轉(zhuǎn)化為實(shí)際物理掩膜版的關(guān)鍵步驟,直接決定了芯片的性能、功耗和面積。本文將引導(dǎo)讀者完成一個(gè)最簡(jiǎn)單但最基礎(chǔ)的數(shù)字單元——CMOS反相器的版圖設(shè)計(jì),使用的工具是行業(yè)標(biāo)準(zhǔn)的Cadence IC(Virtuoso)套件。

一、設(shè)計(jì)準(zhǔn)備與原理回顧

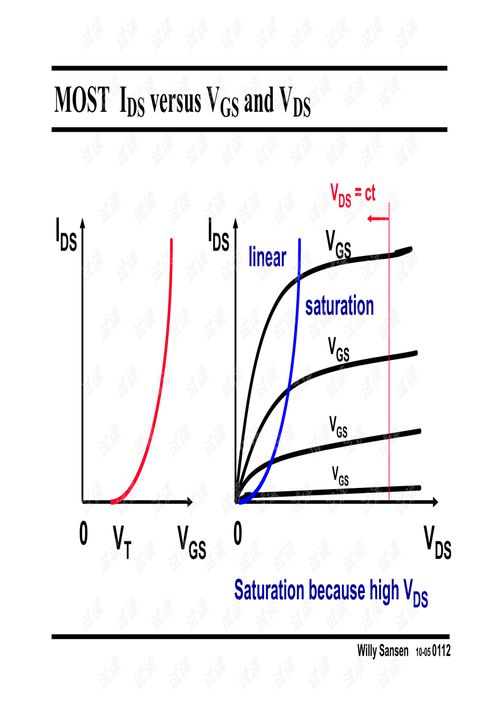

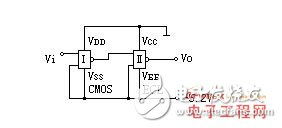

在開(kāi)始版圖設(shè)計(jì)前,我們首先明確設(shè)計(jì)目標(biāo):創(chuàng)建一個(gè)符合設(shè)計(jì)規(guī)則的CMOS反相器版圖。一個(gè)典型的CMOS反相器由一個(gè)PMOS晶體管和一個(gè)NMOS晶體管組成。兩者的柵極相連作為輸入端,漏極相連作為輸出端,PMOS的源極接電源(VDD),NMOS的源極接地(VSS)。

設(shè)計(jì)環(huán)境準(zhǔn)備:確保已啟動(dòng)Cadence IC,并建立了正確配置的設(shè)計(jì)庫(kù)和工藝設(shè)計(jì)套件(PDK)。PDK提供了特定半導(dǎo)體工藝下的設(shè)計(jì)規(guī)則、器件模型和標(biāo)準(zhǔn)單元。

二、版圖設(shè)計(jì)步驟詳解

- 創(chuàng)建版圖單元:在設(shè)計(jì)庫(kù)中,新建一個(gè)

Cell,類型選擇Layout,并命名為inv(或類似名稱)。這將打開(kāi)Virtuoso版圖編輯窗口。

- 繪制有源區(qū)(Active Area):

- 根據(jù)PDK規(guī)則,在

N Well層上繪制一個(gè)矩形,作為PMOS晶體管所在的N阱。

- 然后,分別在N阱內(nèi)部(PMOS區(qū)域)和外部(NMOS區(qū)域)的

Active層(或Diffusion層)繪制兩個(gè)矩形,分別作為PMOS和NMOS的源、漏有源區(qū)。兩者之間需保持足夠的間距。

- 繪制多晶硅柵極(Poly Gate):

- 使用

Poly層,繪制一個(gè)橫跨PMOS和NMOS有源區(qū)的矩形條。這個(gè)多晶硅條就是反相器的公共柵極(輸入端)。多晶硅與有源區(qū)重疊的部分,在后續(xù)工藝中會(huì)形成晶體管的溝道。

- 確保多晶硅的寬度(晶體管的柵長(zhǎng)L)和與有源區(qū)的交疊符合PDK的最小尺寸規(guī)則。

- 進(jìn)行器件標(biāo)識(shí)(注入與選擇層):

- 對(duì)于NMOS區(qū)域:在NMOS的有源區(qū)上覆蓋

N Implant(或N+)層。

- 對(duì)于PMOS區(qū)域(在N阱內(nèi)):在PMOS的有源區(qū)上覆蓋

P Implant(或P+)層。

- 這些層定義了源漏區(qū)的摻雜類型。

- 接觸孔與金屬連線:

- 源/漏接觸:在PMOS和NMOS的有源區(qū)上(避開(kāi)柵極位置),使用

Contact層繪制接觸孔。通常,每個(gè)源/漏區(qū)至少需要兩個(gè)接觸孔以減小電阻。

- 柵極接觸:在柵極多晶硅的延伸部分(未與有源區(qū)重疊處)繪制多晶硅接觸孔。

- 金屬1連線:使用

Metal1層進(jìn)行連接:

- 將PMOS源極的所有接觸孔連接到代表VDD的金屬線。

- 將NMOS源極的所有接觸孔連接到代表VSS(GND)的金屬線。

- 將PMOS和NMOS漏極的接觸孔連接在一起,形成輸出端(OUT)金屬線。

- 將柵極接觸孔連接到輸入端(IN)金屬線。

- 金屬線之間、金屬線與接觸孔之間需滿足最小寬度、最小間距規(guī)則。

- 添加電源/地焊盤與輸入/輸出端口:

- 通常,VDD和VSS線會(huì)畫得較寬以承載電流。

- 使用

Pin工具,在相應(yīng)的金屬層上創(chuàng)建文本標(biāo)簽,例如:VDD、VSS、A(輸入)、Y(輸出),并指定其類型(電源、地、輸入、輸出)。

三、設(shè)計(jì)驗(yàn)證(DRC與LVS)

版圖繪制完成后,絕不能直接用于制造,必須進(jìn)行嚴(yán)格的驗(yàn)證。

- 設(shè)計(jì)規(guī)則檢查(DRC):運(yùn)行DRC,檢查版圖是否完全符合PDK提供的幾何設(shè)計(jì)規(guī)則(如最小線寬、最小間距、最小包圍等)。任何錯(cuò)誤都必須修正,否則芯片無(wú)法被可靠制造。

- 版圖與原理圖一致性檢查(LVS):

- 首先需要有一個(gè)對(duì)應(yīng)的反相器電路原理圖(Schematic)。

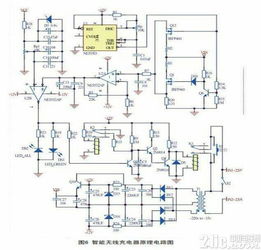

- 運(yùn)行LVS工具,它會(huì)提取版圖中的器件(兩個(gè)MOS管)和連接關(guān)系,并與原理圖進(jìn)行比對(duì)。

- 只有LVS報(bào)告“NETS MATCH”或“CORRECT”,才證明版圖在電氣功能上完全等同于原理圖。

四、與意義

通過(guò)這個(gè)簡(jiǎn)單的反相器版圖設(shè)計(jì),我們實(shí)踐了從有源區(qū)、柵極定義到金屬互連的完整CMOS流程。它雖然基礎(chǔ),但涵蓋了版圖設(shè)計(jì)的核心思想:在嚴(yán)格遵循幾何設(shè)計(jì)規(guī)則(DRC)的前提下,精確實(shí)現(xiàn)預(yù)期的電氣連接(LVS)。

成功的反相器版圖是構(gòu)建更復(fù)雜邏輯門(如與非門、或非門)乃至整個(gè)數(shù)字標(biāo)準(zhǔn)單元庫(kù)的基石。熟練掌握這一過(guò)程,是成為一名合格的數(shù)字集成電路版圖工程師的第一步。后續(xù)的設(shè)計(jì),無(wú)非是在此基礎(chǔ)上增加器件的數(shù)量、優(yōu)化布局以減小面積和寄生效應(yīng),并運(yùn)用更高級(jí)的互連層(Metal2, Metal3...)來(lái)完成復(fù)雜電路的布線。